DDS婎斅偵偁傞僔儕傾儖擖椡偺乮侾乯STB丄乮俀乯DATA丄乮俁乯SCK偺奺抂巕偼丄昞侾偵帵偡傛偆偵PIC16F877偺RE億乕僩懁偵愙懕偟傑偟偨丅PIC16F877偺RE億乕僩偼丄偪傚偆偳億乕僩偑俁偮偁傞偺偱丄偙偙偺億乕僩傪慖傃傑偟偨丅俼俤億乕僩偱側偗傟偽側傜側偄偲偄偆棟桼偼摿偵偁傝傑偣傫丅

![]() 愙懕夞楬偵偮偄偰

愙懕夞楬偵偮偄偰

DDS婎斅偵偁傞僔儕傾儖擖椡偺乮侾乯STB丄乮俀乯DATA丄乮俁乯SCK偺奺抂巕偼丄昞侾偵帵偡傛偆偵PIC16F877偺RE億乕僩懁偵愙懕偟傑偟偨丅PIC16F877偺RE億乕僩偼丄偪傚偆偳億乕僩偑俁偮偁傞偺偱丄偙偙偺億乕僩傪慖傃傑偟偨丅俼俤億乕僩偱側偗傟偽側傜側偄偲偄偆棟桼偼摿偵偁傝傑偣傫丅

| DDS懁偺僔儕傾儖 擖椡抂巕 |

俹俬俠16F877懁偺 愙懕億乕僩 |

| STB | RE0 |

| DATA | RE1 |

| SCK | RE2 |

恾侾偵丄奣棯愙懕恾傪帵偟傑偡丅PIC儕僙僢僩屻丄妋擣偺偨傔 PORTB 偺 LED 偑侾昩娫揰摂偡傞傛偆偵LED傪愙懕偟偰偄傑偡丅RS232C娭楢偺廃曈夞楬偼丄RC7丆RC6億乕僩偵愙懕偟傑偡丅徻嵶偼僔儕傾儖捠怣偺崁栚傪嶲徠偟偰偔偩偝偄丅

|

| 恾侾丏DDS惂屼夞楬偺奣棯愙懕恾 |

![]() DDS惂屼僾儘僌儔儉乮俀乯

DDS惂屼僾儘僌儔儉乮俀乯

恾俀偵DDS偺惂屼僾儘僌儔儉偺僼儘乕僠儍乕僩傪帵偟傑偡丅僾儘僌儔儉偺夝愢偵偮偄偰偼丄乽僾儘僌儔儉偺愢柧乮俀乯乿偺崁傪偛嶲徠偔偩偝偄丅儕僙僢僩屻丄PIC偑摦嶌偟偰偄傞偙偲傪娙扨偵妋擣偡傞偨傔丄PORTB偵愙懕偝傟偨LED偑侾昩娫揰摂偟傑偡丅DSS偺愝掕偱偡偑丄

僷僜僐儞偐傜師偺係偮偺愝掕僨乕僞傪RS232C偱僔儕傾儖憲怣偟傑偡丅

僐儅儞僪僨乕僞係價僢僩偲丄僠僢僾僙儗僋僩僨乕僞俁價僢僩暘偼丄師偺傛偆偵傑偲傔偰憲傝傑偡丅

乮椺乯僠僢僾僙儗僋僩乮CS2=乽俫乿丄CS1=乽俫乿丄CS0=乽俫乿乯乽111乿偱丄僐儅儞僪俠乽1100乿偲偟偨偲偒丄

乽僐儅儞僪僨乕僞乿偲乽僠僢僾僙儗僋僩僨乕僞乿傪傑偲傔偰丄乽1100111乿偲偟傑偡丅偡側傢偪丄俇俈俫偵側傝傑偡丅

師偵廃攇悢僨乕僞偼丄師偺傛偆偵俁偮偵暘妱偟偰憲傝傑偡丅

乮椺乯倖亖10MHz偺廃攇悢偵愝掕偡傞応崌丄侾俇恑昞婰偱峫偊傞偲

10M亖10000000仺俋俉俋俇俉侽俫丂偲側傝傑偡丅

偙偙偱丄俉侽俫偑廃攇悢僨乕僞乮Lower Byte乯偵憡摉丄俋俇俫偑廃攇悢僨乕僞乮Middle Byte乯偵憡摉丄俋俉俫偑廃攇悢僨乕僞乮Higher Byte乯偵憡摉偟傑偡丅

埲忋偺椺偐傜丄僠僢僾僙儗僋僩乮CS2=乽俫乿丄CS1=乽俫乿丄CS0=乽俫乿乯偵愝掕偝傟偨DDS僉僢僩傪丄倖亖10MHz偺廃攇悢偱丄僐儅儞僪俠乮DSS

儊儌儕 1CH 偵廃攇悢僨乕僞傪彂偒崬傒丄偙傟傪弌椡偡傞乯偲偄偆応崌偼丄弴偵俇俈俫丆俉侽俫丆俋俇俫丆俋俉俫偺係偮偺僨乕僞傪憲怣偟傑偡丅

僔儕傾儖憲怣偝傟偨僨乕僞偼PIC懁偱堦搙僶僢僼傽偵奿擺偝傟偨屻丄DDS傊愝掕僨乕僞傪憲傝傑偡丅側偍丄愝掕姰椆屻傕庴怣摦嶌傪懕偗傑偡偺偱丄僷僜僐儞懁偱奺庬僐儅儞僪傗廃攇悢傪怴偨偵愝掕偡傞偙偲傕壜擻偱偡丅

恾俀丏DDS惂屼僾儘僌儔儉偺僼儘乕僠儍乕僩

乮拲乯埲壓偵帵偡僾儘僌儔儉偵偼丄儂乕儉儁乕僕夋柺嶌惉偺搒崌忋丄嬻敀偲偟偰慡妏暥帤偺僗儁乕僗側偳偑憓擖偝傟偰偄傑偡丅偟偨偑偭偰丄壓婰僾儘僌儔儉儕僗僩傪偦偺傑傑僐僺乕偟偰俵俹俴俙俛偺僜乕僗僼傽僀儖偲偝傟偨応崌偵偼丄僄儔乕偲側傞偙偲偑偁傝傑偡丅

仺偙偙傪僋儕僢僋偟偰丄壓婰偺僾儘僌儔儉傪僟僂儞儘乕僪偡傞傛偆偵偟偰偔偩偝偄丅

丂丂![]() 僼傽僀儖柤丗乽dds_2.asm乿丂僒僀僘俈丏俉侾倠僶僀僩

僼傽僀儖柤丗乽dds_2.asm乿丂僒僀僘俈丏俉侾倠僶僀僩

仺偙偙傪僋儕僢僋偟偰丄壓婰偺僆僽僕僃僋僩僼傽僀儖傪僟僂儞儘乕僪偡傞傛偆偵偟偰偔偩偝偄丅

丂丂![]() 僼傽僀儖柤丗乽dds_2.hex乿丂僒僀僘俈侾俈僶僀僩

僼傽僀儖柤丗乽dds_2.hex乿丂僒僀僘俈侾俈僶僀僩

|

;*********************************************************** ; DDS僐儞僩儘乕儖丒僾儘僌儔儉俀 ; ;亂 摦嶌撪梕 亃 ;丂丂PIC儕僙僢僩屻丄妋擣偺偨傔 PORTB 偺 LED 偑侾昩娫揰摂偡傞丅 ;丂丂僷僜僐儞偐傜僠僢僾僙儗僋僩丒僐儅儞僪僨乕僞丄媦傃 ;丂丂廃攇悢僨乕僞傪丄RS232C 僔儕傾儖捠怣偱憲傞丅 ;丂丂廃攇悢僨乕僞偼丄Lower Byte丄Middle Byte丄Higher Byte ;丂丂偺弴偵丄偦傟偧傟 俁暘妱偟偨抣傪憲傞丅 ;丂丂奺僨乕僞偼僶僢僼傽偵堦帪奿擺偟丄僨乕僞偺庴怣偑姰椆偟偨傜丄 ;丂丂悘帪丄DDS 愝掕怣崋傪弌椡偡傞丅 ; ;亂 DDS 愙懕億乕僩 亃 ;丂丂(DDS) 丂丂(PIC) ; 丂丂STB 乧乧乧RE0 ; 丂丂DATA乧乧乧RE1 ; 丂丂SCK 乧乧乧RE2 ; ;亂 RS-232C 愙懕億乕僩 亃 ; 丂旕摨婜幃捠怣儌乕僪 ; 丂儃乕儗乕僩 9600bps ; 丂俉價僢僩丒僲儞僷儕僥傿 ; 丂妱傝崬傒偼巊梡偟側偄 ; ;*********************************************************** |

|

|

丂丂丂丂LIST丂丂丂P=PIC16F877 丂丂丂丂INCLUDE 丂P16F877.INC |

;乮侾乯僾儘僙僢僒偺庬暿巜掕 ;乮俀乯僀儞僋儖乕僪僼傽僀儖偺巜掕 |

|

;*********************************************************** ; 曄悢掕媊偲儗僕僗僞妱晅 ;*********************************************************** |

|

| COUNT 丂丂EQU 丂20H COUNT1丂丂EQU 丂21H COUNT2丂丂EQU 丂22H COUNT3丂丂EQU 丂23H COUNT4丂丂EQU 丂24H TEMP 丂 丂EQU 丂25H COUNT_D 丂EQU 丂26H COUNT_S 丂EQU 丂27H |

;乮俁乯儖乕僾僇僂儞僞 ;丂丂丂儖乕僾僇僂儞僞侾 ;丂丂丂儖乕僾僇僂儞僞俀 ;丂丂丂儖乕僾僇僂儞僞俁 ;丂丂丂儖乕僾僇僂儞僞係 ;丂丂丂堦帪曐娗僨乕僞 ;丂丂丂僨乕僞僇僂儞僞 ;丂丂丂僔僼僩僇僂儞僞 |

|

;*********************************************************** ; 弶婜壔 ; 乮拲乯僶儞僋偺埵抲偵拲堄 ;*********************************************************** |

|

|

丂丂丂丂ORG 丂丂0 丂丂丂丂BSF 丂丂STATUS,RP0 丂丂丂丂MOVLW 丂B'00000010' 丂丂丂丂MOVWF 丂ADCON1 丂丂丂丂CLRF丂丂TRISE 丂丂丂丂CLRF丂丂TRISB 丂丂丂丂MOVLW 丂B'10111111' 丂丂丂丂MOVWF 丂TRISC 丂丂丂丂MOVLW 丂B'00100100' 丂丂丂丂MOVWF 丂TXSTA 丂丂丂丂MOVLW 丂81H 丂丂丂丂MOVWF 丂SPBRG 丂丂丂丂BCF 丂丂STATUS,RP0 丂丂丂丂MOVLW 丂B'10010000' 丂丂丂丂MOVWF 丂RCSTA |

;乮係乯僾儘僌儔儉偺奐巒斣抧偺巜掕 ;乮俆乯Bank 1 傊愗懼 ;乮俇乯RE0,RE1,RE2 僨僕僞儖擖弌椡 ;丂丂丂ADCON1儗僕僗僞偺愝掕 ;乮俈乯PORTE 慡億乕僩傪弌椡偵愝掕 ;乮俉乯PORTB 慡億乕僩傪弌椡偵愝掕 ;乮俋乯RC7/RX乮擖椡乯丆RC6/TX乮弌椡乯 ;乮10乯PORTC 偺愝掕 ;乮11乯8BIT,憲怣嫋壜,旕摨婜,崅懍 ;丂丂丂TXSTA 儗僕僗僞偺愝掕 ;乮12乯儃乕儗乕僩 9600bps (20MHz丗崅懍愝掕帪) ;丂丂丂SPBRG 儗僕僗僞偺愝掕 ;乮13乯Bank 0 傊栠偡 ;乮14乯僔儕傾儖,8BIT,宲懕庴怣嫋壜 ;丂丂丂RCSTA 儗僕僗僞偺愝掕 |

|

;*********************************************************** ; 儊僀儞僾儘僌儔儉 ;*********************************************************** |

|

丂丂丂丂MOVLW 丂B'00000111' 丂丂丂丂MOVWF 丂PORTE MAIN 丂丂丂丂BSF 丂丂STATUS,IRP 丂丂丂丂MOVLW 丂0A0H 丂丂丂丂MOVWF 丂FSR 丂丂丂丂MOVLW 丂4H 丂丂丂丂MOVWF 丂COUNT_D |

;乮15乯DDS怣崋儔僀儞偺儗儀儖偺弶婜愝掕 ;丂丂丂SCK,DATA,STB = [H],[H],[H] 偵愝掕 ;丂丂丂PORTE傊弌椡乮DDS偲偺捠怣偺弶婜愝掕乯 ;乮16乯娫愙傾僪儗僗愝掕 ;丂丂丂僶僢僼傽偺愭摢傾僪儗僗傪僙僢僩偡傞 ;丂丂丂娫愙傾僪儗僗億僀儞僞偺弶婜壔 ;乮17乯4夞孞傝曉偡乮DDS愝掕僨乕僞乯 ;丂丂丂僨乕僞僇僂儞僞偺僙僢僩 |

丂丂丂丂MOVLW 丂B'11111111' 丂丂丂丂MOVWF 丂PORTB 丂丂丂丂CALL丂丂TIME1S 丂丂丂丂MOVLW 丂B'00000000' 丂丂丂丂MOVWF 丂PORTB |

;乮18乯僨乕僞庴怣懸偪偵側偭偰偄傞偙偲傪妋擣偡傞偨傔偺LED昞帵 ;丂丂丂11111111 傪 Wreg 偵儘乕僪偡傞 ;丂丂丂PORTB傊Wreg偺僨乕僞傪弌椡(LED偺揰摂乯 ;乮19乯1昩偺僂僄僀僩傪擖傟傞 ;乮20乯00000000 傪 Wreg 偵儘乕僪偡傞 ;丂丂丂丂PORTB傊Wreg偺僨乕僞傪弌椡(LED偺徚摂乯 |

LPRCV 丂丂丂丂BTFSS 丂PIR1,RCIF 丂丂丂丂GOTO丂丂LPRCV |

;乮21乯USART 庴怣妱傝崬傒僼儔僌價僢僩偺僠僃僢僋 ;丂丂丂PIR1 儗僕僗僞偺 RCIF 偑乽侽乿偩偭偨傜 ;丂丂丂LPRCV 儔儀儖娫傪儖乕僾偡傞 |

丂丂丂丂BTFSC 丂RCSTA,FERR 丂丂丂丂GOTO丂丂FRAME 丂丂丂丂BTFSC 丂RCSTA,OERR 丂丂丂丂GOTO丂丂OVER |

; ****** 僄儔乕僠僃僢僋 ****** ;乮22乯僼儗乕儈儞僌僄儔乕偺僠僃僢僋乮1:僄儔乕,0:惓忢乯 ;丂丂丂僼儗乕儈儞僌僄儔乕帪 FRAME 偺儔儀儖傊僕儍儞僾偡傞 ; ;乮23乯僆乕僶乕儔儞僄儔乕偺僠僃僢僋乮1:僄儔乕,0:惓忢乯 ;丂丂丂僆乕僶乕儔儞僄儔乕帪 OVER 偺儔儀儖傊僕儍儞僾偡傞 |

丂丂丂丂MOVF丂丂RCREG,W 丂丂丂丂MOVWF 丂INDF 丂丂丂丂INCF丂丂FSR,F 丂丂丂丂DECFSZ丂COUNT_D,F 丂丂丂丂GOTO丂丂LPRCV 丂丂丂丂MOVLW 丂0 丂丂丂丂MOVWF 丂INDF |

; ****** 庴怣僨乕僞偺奿擺 ****** ;乮24乯RCREG儗僕僗僞偐傜庴怣僨乕僞傪撉傒崬傓 ;乮25乯僶僢僼傽偵奿擺 ;乮26乯億僀儞僞 亄侾 ;乮27乯僨乕僞僇僂儞僞 亅侾 ;丂丂丂LPRCV 偺儔儀儖傊栠傝孞傝曉偡 ;乮28乯25,24價僢僩栚偺DDS廃攇悢僨乕僞乮忢偵侽乯 ;丂丂丂僶僢僼傽偵奿擺 |

| DDS 丂丂丂丂MOVLW 丂0A0H 丂丂丂丂MOVWF 丂FSR 丂丂丂丂MOVLW 丂5H 丂丂丂丂MOVWF 丂COUNT_D |

; ****** 奿擺僨乕僞偺庢傝偩偟 ****** ;乮29乯僶僢僼傽偺愭摢傾僪儗僗傪僙僢僩偡傞 ;丂丂丂娫愙傾僪儗僗億僀儞僞傪儕僙僢僩偡傞 ;乮30乯5夞孞傝曉偡乮DDS愝掕僨乕僞乯 ;丂丂丂僨乕僞僇僂儞僞偺僙僢僩 |

| DDS_SET 丂丂丂丂MOVF丂丂INDF,W 丂丂丂丂MOVWF 丂TEMP 丂丂丂丂MOVF丂丂COUNT_D,W 丂丂丂丂CALL丂丂TABLE 丂丂丂丂MOVWF 丂COUNT_S |

;乮31乯僶僢僼傽偵奿擺偝傟偰偄傞僨乕僞傪Wreg偵儘乕僪偡傞 ;丂丂丂堦帪曐娗僨乕僞傊 ;乮32乯僨乕僞僇僂儞僞偺抣傪Wreg傊儘乕僪偡傞(OFFSET) ;乮33乯僔僼僩僇僂儞僞抣偺撉傒崬傒僒僽儖乕僠儞傊 ;乮34乯僔僼僩僇僂儞僞偺僙僢僩 |

| DDS_LP 丂丂丂丂RRF 丂丂TEMP,F 丂丂丂丂BTFSS 丂STATUS,C 丂丂丂丂GOTO丂丂DATA_L 丂丂丂丂GOTO丂丂DATA_H |

;乮35乯DDS愝掕僨乕僞傪庢傝弌偡丅 ;乮36乯僨乕僞偑侾偩偭偨傜師偺柦椷傪僗僉僢僾 ;丂丂丂DATA = [L] ;丂丂丂DATA = [H] |

| SET_SCK 丂丂丂丂BCF 丂丂PORTE,2 丂丂丂丂NOP 丂丂丂丂BSF 丂丂PORTE,2 丂丂丂丂DECFSZ丂COUNT_S,F 丂丂丂丂GOTO丂丂DDS_LP 丂丂丂丂INCF丂丂FSR,F 丂丂丂丂DECFSZ丂COUNT_D,F 丂丂丂丂GOTO丂丂DDS_SET |

;乮37乯SCK = [L] ;乮38乯億乕僩偺岆摦嶌杊巭 ;乮39乯SCK = [H] ;乮40乯僔僼僩僇僂儞僞 亅侾 ;丂丂丂DDS_LP 偺儔儀儖傊栠傝孞傝曉偡 ;乮41乯娫愙傾僪儗僗億僀儞僞 亄侾 ;乮42乯僨乕僞僇僂儞僞 亅侾 ;丂丂丂DDS_SET 偺儔儀儖傊栠傝孞傝曉偡 |

丂丂丂丂BSF 丂丂PORTE,1 丂丂丂丂NOP 丂丂丂丂BCF 丂丂PORTE,0 丂丂丂丂NOP 丂丂丂丂BSF 丂丂PORTE,0 丂丂丂丂GOTO丂丂MAIN |

;乮43乯DATA = [H] ;乮44乯億乕僩偺岆摦嶌杊巭 ;乮45乯STB = [L] ;乮46乯億乕僩偺岆摦嶌杊巭 ;乮47乯STB = [H] ;乮48乯孞傝曉偟僨乕僞庴怣摦嶌偵擖傞 |

DATA_L 丂丂丂丂BCF 丂丂PORTE,1 丂丂丂丂GOTO丂丂SET_SCK DATA_H 丂丂丂丂BSF 丂丂PORTE,1 丂丂丂丂GOTO丂丂SET_SCK |

;乮49乯DATA = [L] ;乮50乯DATA = [H] |

|

;*********************************************************** ; 僔僼僩僇僂儞僞丒僥乕僽儖 ;*********************************************************** |

|

| TABLE 丂丂丂丂ADDWF 丂PCL,F 丂丂丂丂NOP 丂丂丂丂DT 丂丂丂2,8,8,8,7 |

;乮51乯TABLE偺掕媊乮PC+OFFSET憡摉偺僔僼僩僇僂儞僞抣傪帩偭偰栠傞乯 ;丂丂丂PC亄OFFSET ;乮52乯僟儈乕僨乕僞 ;乮53乯奺僨乕僞偵懳偡傞僔僼僩僇僂儞僞抣 |

|

;*********************************************************** ; RS232C僔儕傾儖捠怣僄儔乕帪偺張棟 ;*********************************************************** |

|

| FRAME 丂丂丂丂MOVLW 丂B'00001111' 丂丂丂丂MOVWF 丂PORTB 丂丂丂丂CALL丂丂TIME1S 丂丂丂丂MOVLW 丂B'00000000' 丂丂丂丂MOVWF 丂PORTB 丂丂丂丂MOVF丂丂RCREG,W 丂丂丂丂BTFSS 丂RCSTA,OERR 丂丂丂丂GOTO丂丂MAIN |

; 亙僼儗乕儈儞僌僄儔乕帪偺張棟亜 ;乮54乯00001111 傪 Wreg 偵儘乕僪偡傞 ;丂丂丂PORTB傊Wreg偺僨乕僞傪弌椡(LED偺揰摂忬懺偱僄儔乕傪抦傜偣傞乯 ;乮55乯1昩偺僂僄僀僩傪擖傟傞 ;乮56乯00000000 傪 Wreg 偵儘乕僪偡傞 ;丂丂丂PORTB傊Wreg偺僨乕僞傪弌椡(LED偺徚摂乯 ;乮57乯僟儈乕偺擖椡偲FERR僼儔僌傪儕僙僢僩乮RCREG傪儕乕僪偡傞偲僋儕傾乯 ;乮58乯僆乕僶乕儔儞僄儔乕偺僠僃僢僋乮1:僄儔乕,0:惓忢乯 ;丂丂丂僆乕僶乕儔儞僄儔乕偑側偗傟偽 MAIN 偺儔儀儖傊僕儍儞僾偡傞 |

OVER 丂丂丂丂MOVLW 丂B'11110000' 丂丂丂丂MOVWF 丂PORTB 丂丂丂丂CALL丂丂TIME1S 丂丂丂丂MOVLW 丂B'00000000' 丂丂丂丂MOVWF 丂PORTB 丂丂丂丂BCF 丂丂RCSTA,CREN 丂丂丂丂BSF 丂丂RCSTA,CREN 丂丂丂丂GOTO丂丂MAIN |

; 亙僆乕僶乕儔儞僄儔乕帪偺張棟亜 ;乮59乯11110000 傪 Wreg 偵儘乕僪偡傞 ;丂丂丂PORTB傊Wreg偺僨乕僞傪弌椡(LED偺揰摂忬懺偱僄儔乕傪抦傜偣傞乯 ;乮60乯1昩偺僂僄僀僩傪擖傟傞 ;乮61乯00000000 傪 Wreg 偵儘乕僪偡傞 ;丂丂丂PORTB傊Wreg偺僨乕僞傪弌椡(LED偺徚摂乯 ;乮62乯OERR偺儕僙僢僩乮價僢僩CREN 偺僋儕傾偵傛傝僋儕傾偡傞乯 ;乮63乯楢懕庴怣傪嫋壜偡傞 ;乮64乯MAIN 偺儔儀儖傊僕儍儞僾偡傞 |

| ;*********************************************************** ;抶墑僒僽儖乕僠儞 ;*********************************************************** ;侾侽侽兪倱抶墑僒僽儖乕僠儞乮俀侽俵俫倸僋儘僢僋帪乯 ;丒丒丒丒丒暿婰僾儘僌儔儉儕僗僩嶲徠丒丒丒丒丒 ; ;侾侽倣倱抶墑僒僽儖乕僠儞乮俀侽俵俫倸僋儘僢僋帪乯 ;丒丒丒丒丒暿婰僾儘僌儔儉儕僗僩嶲徠丒丒丒丒丒 ; ;侾倱抶墑僒僽儖乕僠儞乮俀侽俵俫倸僋儘僢僋帪乯 ;丒丒丒丒丒暿婰僾儘僌儔儉儕僗僩嶲徠丒丒丒丒丒 |

|

丂丂丂丂END |

丂 |

亂僾儘僌儔儉偺愢柧乮俀乯亃![]()

偙偺僾儘僌儔儉偵偮偄偰丄弴傪捛偭偰夝愢傪壛偊偰偍偒傑偟傚偆丅

乮侾乯僾儘僙僢僒偺庬暿巜掕

掕媊偺巇曽偼乽PROCESSOR乿偐乽LIST乿柦椷傪巊偭偰愝掕偟傑偡丅偙偙偱巜掕偡傞僾儘僙僢僒柤徧偼丄僷僢働乕僕偺庬椶傪帵偡僒僼傿僢僋僗乮嵟屻偺塸婰崋偺晹暘乯偼晄梫偱偡丅

丂丂丂PROCESSOR丂丂PIC16F877

丂丂丂丂傑偨偼

丂丂丂LIST丂丂P=PIC16F877

乮俀乯昗弨僿僢僟乕僼傽僀儖偺僀儞僋儖乕僪

昗弨僿僢僟乕僼傽僀儖偲偼丄奺僾儘僙僢僒偑帩偭偰偄傞俽俥俼乮Special Function Register乯傪儔儀儖乮婰崋乯偱巊偊傞

偨傔丄儔儀儖偲僴乕僪僂僃傾偺応強偲傪掕媊偟偰偄傞僼傽僀儖偱偡丅昗弨僿僢僟乕僼傽僀儖偼丂乽僾儘僙僢僒柤丏INC乿偲偄偆僼傽僀儖柤偱摑堦偝傟偰丄MPLAB偺僨傿儗僋僩儕偵奿擺偝傟偰偄傑偡丅廬偭偰丄偙傟偺僀儞僋儖乕僪曽朄偼壓婰偺傛偆偵偟偰峴偄傑偡丅

堦搙丄嶲峫傑偱偵昗弨僿僢僟乕僼傽僀儖偺撪梕傪僄僨傿僞摍偱尒偰偍偔偙偲傪偍姪傔偟傑偡丅

丂丂丂INCLUDE 丂丂丂P16F877.INC

丂丂丂丂傑偨偼

丂丂丂#INCLUDE丂丂丂P16F877.INC

乮俁乯曄悢掕媊偲儗僕僗僞妱晅

儗僕僗僞僼傽僀儖傾僪儗僗傪巜掕偡傞偲偒偵丄傾僪儗僗悢抣傪捈愙巜掕偡傞偙偲傕偱偒傑偡偑丄悢抣偩偗偱偼娫堘偄傕懡偔丄僾儘僌儔儉帺恎傕暘偐傝偵偔偔側偭偰偟傑偄傑偡丅偦偙偱丄俤俻倀柦椷側偳傪巊偭偰儔儀儖傪愝掕偟曄悢傪掕媊偟傑偡丅儗僕僗僞僼傽僀儖傾僪儗僗偼丄俈價僢僩偁傞偺偱丄侽侽乣俈俥傑偱嵟戝侾俀俉屄偺儗僕僗僞偑巜掕偱偒傑偡偑丄幚嵺偵暔棟揑偵幚憰偝傟偰斈梡揑偵巊梡偱偒傞儗僕僗僞悢偼僨僶僀僗偵傛偭偰堎側偭偰偄傑偡偺偱拲堄偑昁梫偱偡丅

俹俬俠侾俇俥俉俈俈偺斈梡儗僕僗僞偺傾僪儗僗偼丄俀侽俫乣俈俥俫

偲側偭偰偄傑偡偺偱丄俀侽俫埲崀偺傾僪儗僗偵妱傝晅偗傑偡丅

乮係乯僾儘僌儔儉偺奐巒斣抧偺巜掕

乽ORG乿偼僾儘僌儔儉偺奐巒斣抧傪巜掕偡傞媅帡柦椷偱丄ORG埲壓偺幚嵺偺僾儘僌儔儉柦椷偑奿擺偝傟傞僾儘僌儔儉儊儌儕撪偺埵抲乮傾僪儗僗乯傪巜掕偟傑偡丅

丂丂丂ORG丂丂0丂丂;0斣抧偐傜奿擺偡傞偙偲傪帵偟傑偡丅

僐儞僺儏乕僞偼堦斒偵揹尮搳擖帪傗儕僙僢僩傪偡傞偲昁偢0斣抧偐傜僗僞乕僩偡傞傛偆偵側偭偰偄傞偺偱丄0斣抧偵偼昁偢柦椷偑偁傞偙偲偑昁梫偱偡丅

乮俆乯Bank 1 傊愗懼

PIC偵偼奺庬偺摦嶌儌乕僪傪愝掕偡傞偨傔偺 Special

Register 偲屇偽傟傞傕偺偑梡堄偝傟偰偄傑偡丅PIC傪摦嶌偝偣傞偨傔偵偼丄傑偢偙偺Special

Register偺愝掕偐傜巒傔傑偡丅偦偟偰偦傟傜偼慡偰丄Register

File 偲屇傇儊儌儕偲偟偰梡堄偝傟偰偄傑偡丅偦偺

Register File偼 Bank0, Bank1, Bank2, Bank3

偲傛偽傟傞傾僪儗僗嬻娫傪傕偭偰偄傞偨傔丄懡彮傾僋僙僗偺巇曽偑柺搢偱偡丅偮傑傝RESET屻偺捠忢偼Bank0偲側偭偰偄傞偺偱丄Bank1懁偺儗僕僗僞偵傾僋僙僗偡傞偲偒偼Bank偺愗懼偊傪偟偰偐傜偲側傝傑偡丅傑偨Bank0偲Bank1偵摨偠暔偑偁傞偲偒偵偼偳偪傜偱傕摨偠條偵巊偊傑偡丅

Bank1傊愗傝懼偊傞曽朄偱偡偑丄乽STATUS乿儗僕僗僞偵偁傞俀價僢僩偺RP0丄RP1傪曄偊偰Bank傪巜掕偟傑偡丅僨僼僅儖僩偼丄Bank0偱偡丅昞俀偵俛倎値倠偲俼俹侾丆俼俹侽價僢僩偲偺娭學傪帵偟傑偡丅Bank1傊愗傝懼偊傞偨傔偵偼丄俼俹侽價僢僩傪乽侾乿偵偟傑偡丅乮俼俹侾偼僨僼僅儖僩偱乽侽乿側偺偱曄偊傞昁梫偼側偄丅乯

丂BSF丂丂丂丂STATUS,RP0

乽俽俿俙俿倀俽乿儗僕僗僞偺俼俹侽價僢僩傪乽侾乿偵偡傞丅

| 俛倎値倠 | 俼俹侾 | 俼俹侽 |

| 侽 | 侽 | 侽 |

| 侾 | 侽 | 侾 |

| 俀 | 侾 | 侽 |

| 俁 | 侾 | 侾 |

乮俇乯RE0,RE1,RE2 僨僕僞儖擖弌椡

丂丂丂ADCON1儗僕僗僞偺愝掕

![]()

RE億乕僩傪僨傿僕僞儖擖弌椡億乕僩偲偟偰巊梡偡傞偨傔偵偼丄ADCON1儗僕僗僞偺愝掕偑昁梫

RE億乕僩傪僨傿僕僞儖擖弌椡億乕僩偲偟偰巊梡偡傞偨傔偵偼丄ADCON1儗僕僗僞偺愝掕偑昁梫偵側傝傑偡丅PIC偺儕僙僢僩屻偼丄RE億乕僩偑A/D曄姺偺擖椡億乕僩偵側偭偰偄傞偐傜偱偡丅乮RA億乕僩傕摨條乯俙俢俠俷俶侾儗僕僗僞偺俁乣侽價僢僩乮俹俠俥俧倶乯偺愝掕撪梕傛傝寛掕偟傑偡丅PCFGx亖乽0010乿

or 乽0011乿 or 乽0100乿 or 乽0101乿 or 乽0110乿 or 乽0111乿 or 乽1100乿

or 乽1101乿 or 乽1110乿 or 乽1111乿偺偄偢傟偐偺偲偒RE億乕僩偼僨傿僕僞儖擖弌椡億乕僩偵側傞偙偲偑暘偐傝傑偡丅乮偙偺偲偒丄RA億乕僩偼巊梡偟側偄偺偱丄RA億乕僩偺愝掕偼柍娭學偲偟傑偡乯

ADCON1儗僕僗僞偺愝掕撪梕偺徻嵶偼丄偙偪傜傪偛棗偔偩偝偄丅仺ADCON1儗僕僗僞偺愝掕撪梕偵偮偄偰

側偍丄俙俢俠俷俶侾儗僕僗僞偺俈乣係價僢僩偼丄娙扨偺偨傔偲傝偁偊偢乽侽乿偲偱傕偟偰偍偒丄傑偨PCFGx亖乽0010乿偲偡傞偙偲偱丄偡側傢偪丄乽ADCON1仺俛乫侽侽侽侽侽侽侾侽乫丂乮俀俫乯乿偵愝掕偡傞偙偲偱丄RE億乕僩傪僨傿僕僞儖擖弌椡億乕僩偲偟偰巊梡偡傞偙偲偑偱偒傑偡丅

乮俈乯PORTE 慡億乕僩傪弌椡偵愝掕

俿俼俬俽俤儗僕僗僞傪丄俠俴俼俥乮倖儗僕僗僞傪僛儘僋儕傾偡傞柦椷乯偱弌椡愝掕偲偟傑偡丅

丂CLRF丂丂丂TRIS俤

乽俿俼俬俽俤儗僕僗僞傪僛儘僋儕傾偡傞丅偡側傢偪丄俹俷俼俿俤慡億乕僩傪弌椡偵愝掕偡傞乿

乮俉乯PORTB 慡億乕僩傪弌椡偵愝掕

俿俼俬俽俛儗僕僗僞傪丄俠俴俼俥乮倖儗僕僗僞傪僛儘僋儕傾偡傞柦椷乯偱弌椡愝掕偲偟傑偡丅

丂CLRF丂丂丂TRISB

乽俿俼俬俽B儗僕僗僞傪僛儘僋儕傾偡傞丅偡側傢偪丄俹俷俼俿俛慡億乕僩傪弌椡偵愝掕偡傞乿

PORT俛偵偼俴俤俢偑愙懕偝傟偰偍傝丄DDS傊僔儕傾儖擖椡偡傞忬懺偵擖偭偨偲偒偺妋擣偺偨傔偵丄揰摂偡傞傛偆偵偟偰偄傑偡丅

乮俋乯RC7/RX乮擖椡乯丆RC6/TX乮弌椡乯

僔儕傾儖捠怣偺擖弌椡億乕僩偲偟偰丄庴怣擖椡億乕僩(RC7/RX)偲丄憲怣弌椡億乕僩(RC6/TX)傪巊偄傑偡丅懠偺俼俠億乕僩偼巊偄傑偣傫偺偱丄偲傝偁偊偢擖椡偵愝掕偟偰偍偒傑偡丅偟偨偑偭偰丄俼俠俇偺傒弌椡愝掕偵偟傑偡丅

偲偄偆偙偲偱丄俛乫侾侽侾侾侾侾侾侾乫丂乮俛俥俫乯傪倂倰倕倗偵儘乕僪偡傞丅

乮侾侽乯PORTC 偺愝掕

倂倰倕倗偺撪梕傪TRISC儗僕僗僞偵忋彂偒偡傞丅

乮侾侾乯8BIT,憲怣嫋壜,旕摨婜,崅懍丆TXSTA 儗僕僗僞偺愝掕

乽僔儕傾儖捠怣婡擻乿偺惂屼梡儗僕僗僞偺夝愢崁栚偱TXSTA儗僕僗僞傪嶲徠偟偰偔偩偝偄丅

TXSTA儗僕僗僞偺撪梕

偲偄偆偙偲偱丄TXSTA仺俛乫侽侽侾侽侽侾侽侽乫丂乮俀係俫乯

乮侾俀乯儃乕儗乕僩 9600bps (20MHz丗崅懍愝掕帪), SPBRG 儗僕僗僞偺愝掕

乽僔儕傾儖捠怣婡擻乿偺SPBREG儗僕僗僞偺夝愢崁栚偱昞俁丏SPBRG偺愝掕抣偲儃乕儗乕僩傪嶲徠偟偰偔偩偝偄丅儃乕儗乕僩傪俋俇侽侽倐倫倱偵愝掕偟傑偡丅昞俁亅侾偺掅懍儌乕僪傗丄昞俁亅俀偺崅懍儌乕僪偑偁傝傑偡偑丄偙偙偱偼崅懍儌乕僪偺俋俇侽侽倐倫倱傪慖戰偟傑偡丅僋儘僢僋廃攇悢偑俀侽俵俫倸偺応崌偼丄掅懍儌乕僪傛傝崅懍儌乕僪偺曽偑僄儔乕儗乕僩偑彫偝偄偨傔偱偡丅偟偨偑偭偰丄崅懍儌乕僪偺応崌偺SPBREG偼丄俉侾俫偵愝掕偡傟偽傛偄偙偲偑暘偐傝傑偡丅

乮拲乯MicroChip幮偺僨乕僞僔乕僩偼丄SPBREG偺愝掕昞帵偼侾侽恑悢(decimal)偵側偭偰偄傑偡偺偱拲堄偟偰偔偩偝偄丅

乮侾俁乯Bank 0 傊栠偡

俛倎値倠侾偱偺愝掕偑廔椆偟偨屻偼丄俛倎値倠侽偵栠偟偰偍偒傑偡丅Bank1傊愗傝懼偊傞偨傔偵偼丄俼俹侽價僢僩傪乽侽乿偵偟傑偡丅乮俼俹侾偼僨僼僅儖僩偱乽侽乿側偺偱曄偊傞昁梫偼側偄丅乯

BCF丂丂丂丂STATUS,RP0

乽俽俿俙俿倀俽乿儗僕僗僞偺俼俹侽價僢僩傪乽侽乿偵偡傞丅偡側傢偪丄俛倎値倠侽偵栠偡丅乿

乮侾係乯僔儕傾儖,8BIT,宲懕庴怣嫋壜丆RCSTA 儗僕僗僞偺愝掕

乽僔儕傾儖捠怣婡擻乿偺惂屼梡儗僕僗僞偺夝愢崁栚偱RCSTA儗僕僗僞傪嶲徠偟偰偔偩偝偄丅

RCSTA儗僕僗僞偺撪梕偺寛掕

偲偄偆偙偲偱丄RCSTA仺俛乫侾侽侽侾侽侽侽侽乫丂乮俋侽俫乯

乮侾俆乯DDS怣崋儔僀儞偺儗儀儖偺弶婜愝掕

丂丂丂SCK,DATA,STB = [H],[H],[H] 偵愝掕丆PORTE傊弌椡乮DDS偲偺捠怣偺弶婜愝掕乯

DDS偲偺僔儕傾儖捠怣傪峴偆慜偵丄怣崋儔僀儞乮SCK丆DATA丆STB乯傪偡傋偰乽俫乿偵弶婜愝掕偟偰偍偒傑偡丅

乮侾俇乯娫愙傾僪儗僗愝掕丂![]()

僶僢僼傽偺愭摢傾僪儗僗傪僙僢僩丂娫愙傾僪儗僗億僀儞僞偺弶婜壔

僨乕僞儊儌儕偺傾僋僙僗曽朄偵丄捈愙儗僕僗僞偺傾僪儗僗傪巜掕偟偰傾僋僙僗偡傞捈愙傾僪儗僢僔儞僌偺傎偐偵丄娫愙傾僪儗僢僔儞僌偲偄偆曽朄偑偁傝傑偡丅娫愙傾僪儗僢僔儞僌偼丄FSR儗僕僗僞乮File

Selection Register乯偲丄STATUS儗僕僗僞拞偺IRP價僢僩傪巊偄傑偡丅偙偺FSR儗僕僗僞偑僾儘僌儔儉拞偱帺桼偵彂偒姺偊傜傟傞偺偱丄僾儘僌儔儉拞偵僶僢僼傽側偳傪嶌偭偰楢懕偟偨椞堟傪弴偵傾僋僙僗偡傞偺偵曋棙偵巊偊傑偡丅傑偨丄娫愙傾僪儗僢僔儞僌偱巜掕偝傟偨僨乕僞儊儌儕偼丄INDF儗僕僗僞傪宱桼偟偰娫愙揑偵傾僋僙僗偟傑偡丅偡側傢偪丄巜掕偟偨僨乕僞儊儌儕偵彂偒崬傓応崌偵偼丄INDF儗僕僗僞偵彂偒崬傒丄巜掕偟偨僨乕僞儊儌儕偺撪梕傪撉傒弌偡偲偒偵偼丄INDF儗僕僗僞偺撪梕傪撉傒崬傒傑偡丅

恾俁偵娫愙傾僪儗僢僔儞僌偱偺僨乕僞儊儌儕丒傾僪儗僗巜掕偵偮偄偰偺夝愢恾傪帵偟傑偡丅

|

| 恾俁丏娫愙傾僪儗僢僔儞僌偺僨乕僞儊儌儕丒傾僪儗僗巜掕偵偮偄偰 |

乮僾儘僌儔儉椺乯Bank3偺斈梡僨乕僞儊儌儕偺傾僪儗僗20H傪巜掕偟偨偄偲偒

STATUS儗僕僗僞偺RP0,RP1傪巊偭偰Bank偺愗傝懼偊傪偡傞昁梫偼偁傝傑偣傫丄師偺傛偆偵捈愙擟堄偺Bank傪傾僋僙僗偟傑偡丅恾俀偺Bank巜掕偐傜丄STATUS儗僕僗僞偺IRP傪乽侾乿丄FSR儗僕僗僞偺俈價僢僩栚傪乽侾乿偵偟傑偡丅

傑偨丄応強傾僪儗僗偺巜掕偐傜FSR儗僕僗僞偺俇乣侽價僢僩栚傪丄20H偵偟傑偡偑丄俈價僢僩栚偑乽侾乿偵側偭偰偄傑偡偺偱丄FSR儗僕僗僞偼丄A0俫偵偟傑偡丅偟偨偑偭偰丄

BSF 丂丂丂丂STATUS,IRP丂丂丟STATUS儗僕僗僞偺IRP價僢僩傪乽侾乿偵偡傞丅

MOVLW 丂丂0A0H丂丂丂丂丂丂丟A0H傪Wreg儗僕僗僞偵儘乕僪偡傞

MOVWF 丂丂FSR丂丂丂丂丂丂丂丟Wreg儗僕僗僞偺撪梕傪FSR儗僕僗僞偵奿擺偡傞丅

偲側傝傑偡丅

乮侾俈乯4夞孞傝曉偡乮DDS愝掕僨乕僞乯丆僨乕僞僇僂儞僞偺僙僢僩

僷僜僐儞偐傜 RS232C 僔儕傾儖捠怣偵偰丄師偺侾乣係傑偱偺奺僨乕僞偑弴偵憲傜傟偰偔傞偺偱丄庴怣摦嶌傪係夞孞傝曉偡傛偆偵僨乕僞僇僂儞僞傪僙僢僩偟傑偡丅

乮侾俉乯僨乕僞庴怣懸偪偵側偭偰偄傞偙偲傪妋擣偡傞偨傔偺LED昞帵

丂丂丂丂11111111 傪 Wreg 偵儘乕僪偟丄PORTB傊Wreg偺僨乕僞傪弌椡(LED偺慡揰摂乯

偙偙偱丄儗僕僗僞偺弶婜愝掕偑廔椆偟丄僷僜僐儞偐傜偺僨乕僞擖椡懸偪乮庴怣忬懺乯偵擖偭偨偙偲傪妋擣偡傞偨傔丄

PORTB 偺 LED 傪慡揰摂偝偣傞傛偆偵偟傑偡丅

乮侾俋乯1昩偺僂僄僀僩傪擖傟傞

PORTB 偺 LED 偺揰摂帪娫傪侾昩娫偵愝掕偟傑偡丅偙偙偱偼丄抶墑僒僽儖乕僠儞傪巊偭偰偄傑偡丅

乮俀侽乯00000000 傪 Wreg 偵儘乕僪偟丄

丂丂丂丂PORTB傊Wreg偺僨乕僞傪弌椡(LED偺徚摂乯

揰摂偟偰偄偨俴俤俢傪徚摂偝偣丄僨乕僞偺庴怣忬懺偵擖傝傑偡丅

乮俀侾乯USART 庴怣妱傝崬傒僼儔僌價僢僩偺僠僃僢僋乮1:USART 庴怣僶僢僼傽偑僼儖,

0:嬻乯

丂丂丂丂庴怣僶僢僼傽偑嬻偱偁傟偽 LPRCV 偺儔儀儖娫傪孞傝曉偡

廃曈婡擻偺妱傝崬傒偺僼儔僌價僢僩偑妱傝摉偰傜傟偰偄傞PIR1儗僕僗僞偺USART

庴怣妱傝崬傒僼儔僌價僢僩乮RCIF乯偺忬懺傪僠僃僢僋偟傑偡丅

USART庴怣僶僢僼傽偑僼儖偱偁傞偲偡傞偲丄RCIF偑乽侾乿偲側傝丄師偺柦椷偱暘婒偝傟傑偡丅

BTFSS 丂丂PIR1,RCIF

乽PIR1乿儗僕僗僞偺RCIF價僢僩偑乽侾乿偩偭偨傜師偺柦椷傪僗僉僢僾偟丄儖乕僾偐傜敳偗傑偡丅

GOTO丂丂丂LPRCV

偨偩偟丄庴怣僶僢僼傽偑嬻偺娫偼丄乽PIR1乿儗僕僗僞偺RCIF價僢僩偑乽侽乿偺傑傑偱偡偺偱丄LPRCV儔儀儖傊栠偭偰儖乕僾傪孞傝曉偟傑偡丅

乮俀俀乯僼儗乕儈儞僌僄儔乕偺僠僃僢僋乮1:僄儔乕,0:惓忢乯

庴怣僗僥乕僞僗偍傛傃僐儞僩儘乕儖儗僕僗僞偱偁傞RCSTA儗僕僗僞偺僼儗乕儈儞僌僄儔乕價僢僩乮FERR乯偺忬懺傪僠僃僢僋偟傑偡丅

BTFSC 丂丂RCSTA,FERR

乽RCSTA乿儗僕僗僞偺FERR價僢僩偑惓忢偺乽侽乿偩偭偨傜師偺柦椷傪僗僉僢僾偟丄僆乕僶乕儔儞僄儔乕偺僠僃僢僋傊恑傒傑偡丅

GOTO丂丂丂FRAME

僼儗乕儈儞僌僄儔乕帪 FRAME 偺儔儀儖傊僕儍儞僾偟傑偡丅

乮俀俁乯僆乕僶乕儔儞僄儔乕偺僠僃僢僋乮1:僄儔乕,0:惓忢乯

庴怣僗僥乕僞僗偍傛傃僐儞僩儘乕儖儗僕僗僞偱偁傞RCSTA儗僕僗僞偺僆乕僶乕儔儞僄儔乕價僢僩乮OERR乯偺忬懺傪僠僃僢僋偟傑偡丅

BTFSC 丂丂RCSTA,OERR

乽RCSTA乿儗僕僗僞偺OERR價僢僩偑惓忢偺乽侽乿偩偭偨傜師偺柦椷傪僗僉僢僾偟丄庴怣僨乕僞偺奿擺傊恑傒傑偡丅

GOTO丂丂丂OVER

僆乕僶乕儔儞僄儔乕帪 OVER偺儔儀儖傊僕儍儞僾偟傑偡丅

乮俀係乯RCREG儗僕僗僞偐傜庴怣僨乕僞傪撉傒崬傓

RCREG儗僕僗僞乮庴怣僨乕僞偑奿擺偝傟偰偄傞乯撪梕傪Wreg傊儘乕僪偡傞丅

乮俀俆乯僶僢僼傽偵奿擺

僨乕僞儊儌儕偵彂偒崬傓応崌偵偼丄INDF儗僕僗僞傪宱桼偟偰娫愙揑偵彂偒崬傒傑偡丅

MOVWF 丂丂INDF

INDF儗僕僗僞偵Wreg偺撪梕傪奿擺乮仺娫愙傾僪儗僢僔儞僌偱巜掕偟偨僨乕僞儊儌儕偵奿擺偝傟傞乯

乮俀俇乯億僀儞僞 亄侾

僶僢僼傽偺娫愙傾僪儗僗億僀儞僞傪亄侾偵偟偰丄師偺傾僪儗僗傪巜掕偟傑偡丅

乮俀俈乯僨乕僞僇僂儞僞 亅侾丆丂LPRCV 偺儔儀儖傊栠傝孞傝曉偡

僷僜僐儞偐傜 RS232C 僔儕傾儖捠怣偵偰丄係Byte暘偺僨乕僞偑弴偵憲傜傟偰偔傞偺偱丄乮侾俈乯偱係夞孞傝曉偡傛偆偵僙僢僩偝傟偨僨乕僞僇僂儞僞傪亅侾偢偮尭傜偟丄侽偵側傞傑偱LPRCV娫偺庴怣摦嶌傪孞傝曉偟傑偡丅

乮俀俉乯24丆25價僢僩栚偺DDS廃攇悢僨乕僞乮忢偵侽乯丆僶僢僼傽偵奿擺

偙傟傑偱僷僜僐儞偐傜偼 RS232C 僔儕傾儖捠怣偵偰丄僠僢僾僙儗僋僩仌僐儅儞僪僨乕僞丄侽價僢僩栚乣23價僢僩栚傑偱偺廃攇悢僨乕僞乮壓婰偵帵偡侾乣係傑偱偺僨乕僞乯偑僶僢僼傽偵奿擺偝傟傑偟偨丅DDS偺廃攇悢僨乕僞偼侽價僢僩乣25價僢僩偱峔惉偝傟偰偄傞偨傔丄偙偙偱24丆25價僢僩栚偺DDS廃攇悢僨乕僞傕僶僢僼傽偵奿擺偟傑偡丅偨偩偟丄DDS偺愝掕巇條偐傜24丆25價僢僩栚偺僨乕僞偵偮偄偰偼丄忢偵侽偱偡偺偱丄偁偊偰僔儕傾儖捠怣偱偙偺晹暘偺僨乕僞傪憲傞昁梫偼偁傝傑偣傫丅

乮俀俋乯僶僢僼傽偺愭摢傾僪儗僗傪僙僢僩偡傞丆娫愙傾僪儗僗億僀儞僞傪儕僙僢僩偡傞

僨乕僞偺庢傝弌偟儖乕僠儞偵擖偭偨偲偒丄奿擺偝傟偰偄傞僶僢僼傽偺愭摢偵娫愙傾僪儗僗億僀儞僞傪僙僢僩偟傑偡丅

STATUS儗僕僗僞偺IRP偼乽侾乿偺傑傑曄壔偟偰偄傑偣傫偺偱丄偁偊偰僙僢僩偡傞昁梫偼偁傝傑偣傫丅FSR偺愝掕傪乮侾俇乯偺崁栚偲摨偠A0H偵僙僢僩偟傑偡丅

乮俁侽乯5夞孞傝曉偡乮DDS愝掕僨乕僞乯丆僨乕僞僇僂儞僞偺僙僢僩

(28)偱僶僢僼傽偵彂偒崬傑傟偨侾乣俆傑偱偺俆偮偺僨乕僞傪庢傝弌偡偨傔丄摦嶌傪俆夞孞傝曉偡傛偆偵僨乕僞僇僂儞僞傪僙僢僩偟傑偡丅

乮俁侾乯僶僢僼傽偵奿擺偝傟偰偄傞僨乕僞傪Wreg偵儘乕僪偡傞丆堦帪曐娗僨乕僞傊

僶僢僼傽偵彂偒崬傑傟偨僨乕僞傪撉傒崬傓応崌偵偼丄INDF儗僕僗僞傪宱桼偟偰娫愙揑偵撉傒崬傒傑偡丅撉傒崬傑傟偨僨乕僞偼丄TEMP儗僕僗僞偵堦帪曐娗偟偰偍偒傑偡丅

乮俁俀乯僨乕僞僇僂儞僞偺抣傪Wreg傊儘乕僪偡傞(OFFSET)

僥乕僽儖偵婰嵹偝傟偰偄傞僔僼僩僇僂儞僞抣傪撉傒崬傫偱偔傞偨傔丄僨乕僞僇僂儞僞偺抣傪Wreg偵儘乕僪偟傑偡丅偙偺僨乕僞僇僂儞僞偺抣偼丄僾儘僌儔儉僇僂儞僞偵僨乕僞僇僂儞僞偺抣乮OFFSET暘乯傪懌偟崌傢偣傞偙偲偱丄僔僼僩僇僂儞僞抣偑婰嵹偝傟偨僥乕僽儖偺埵抲娭學傪巜偟帵偡傛偆偵側偭偰偄傑偡丅

乮俁俁乯僔僼僩僇僂儞僞抣偺撉傒崬傒僒僽儖乕僠儞傊

僔僼僩僇僂儞僞抣傪撉傒崬傓僒僽儖乕僠儞傊旘傃傑偡丅

乮俁係乯僔僼僩僇僂儞僞偺僙僢僩

撉傒崬傑傟偨僔僼僩僇僂儞僞偺抣傪僙僢僩偟傑偡丅

乮俁俆乯DDS愝掕僨乕僞傪庢傝弌偡

TEMP儗僕僗僞偵堦帪曐娗偝傟偨DDS愝掕僨乕僞偺撪梕傪丄侾價僢僩僉儍儕傪娷傔偰塃偵堏摦偝偣丄偦偺寢壥傪TEMP儗僕僗僞偵忋彂偒偟傑偡丅偙偺偲偒TEMP儗僕僗僞偺LSB偺價僢僩乮侽

or 侾乯偵傛偭偰俠僼儔僌偑曄壔偟傑偡偺偱丄師偺忦審暘婒偱壓埵偐傜侾價僢僩暘偢偮DDS偺愝掕僨乕僞傪庢傝弌偡偙偲偑偱偒傑偡丅

乮俁俇乯僨乕僞偑侾偩偭偨傜師偺柦椷傪僗僉僢僾

丂丂丂DATA = [L]丂偐丂DATA = [H] 偐偺忦審暘婒

侾價僢僩暘偺撉傒崬傑傟偨僨乕僞偑丄侾偩偭偨傜DDS傊偺DATA怣崋儔僀儞傪[H]偵丄侽偩偭偨傜DDS傊偺DATA怣崋儔僀儞傪[俴]偵偡傞忦審暘婒偵側傝傑偡丅

乮俁俈乯SCK = [L]

DDS傊偺SCK怣崋儔僀儞傪[俴]偵偟傑偡丅

乮俁俉乯億乕僩偺岆摦嶌杊巭

![]()

BSF丆BCF側偳偺價僢僩憖嶌柦椷偱丄摨偠億乕僩偵弌椡偡傞応崌偵偼丄娫偵僟儈乕偲偟偰NOP柦椷側偳傪擖傟傞

偙偙偼丄乮俁俈乯偲乮俁俋乯偺傛偆偵丄BSF丆BCF側偳偺價僢僩憖嶌柦椷偵傛傝摨堦億乕僩傪懕偗偰愝掕偟偰偄傞偲丄億乕僩偑岆摦嶌傪偡傞偙偲偑偁傞偺偱丄僟儈乕偲偟偰俶俷俹傪擖傟偰偄傑偡丅BSF丆BCF側偳偺價僢僩憖嶌柦椷偼丄堦搙億乕僩儗僕僗僞偺偡傋偰偺價僢僩偺忬懺傪撉傒崬傒丄巜掕價僢僩偺傒傪曄峏偟偰嵞搙億乕僩儗僕僗僞偵忋彂偒偡傞偲偄偆憖嶌偑偝傟傑偡丅偡側傢偪丄嵟弶偺柦椷乮俁俈乯偺弌椡偑側偝傟丄師偺柦椷乮俁俋乯偑弌椡偝傟傞慜偵丄堦搙擖椡摦嶌偑偁傞偺偱偡丅嵟弶偺柦椷偺弌椡偲師偺柦椷偺擖椡摦嶌偺娫偼丄侾僋儘僢僋暘偟偐側偔丄俀侽俵俫倸僋儘僢僋偺応崌偵偼傢偢偐偵50nsec偱偡丅弌椡僺儞偺晧壸偵壗傜偐偺梕検惉暘偑偁傞偲丄怣崋偺棫偪忋偑傝傗棫偪壓偑傝偑抶傟傞偨傔丄嵟弶偺柦椷偺弌椡偑姰慡偵棊偪拝偔慜偵師偺柦椷偱撉傒崬傒傪幚峴偟偰偟傑偆偨傔岆摦嶌偑敪惗偟傗偡偔側傝傑偡丅偙偺懳嶔偲偟偰偼丄價僢僩憖嶌柦椷偱楢懕偟偰摨偠億乕僩偵弌椡偡傞応崌偵偼丄娫偵NOP柦椷側偳懠偺柦椷傪嵟掅侾屄憓擖偡傞傛偆偵偟傑偡丅

乮俁俋乯SCK = [H]

DDS傊偺SCK怣崋儔僀儞傪[俫]偵偟傑偡丅偙偺偲偒丄SCK偺棫偪忋偑傝偱DATA偑撉傒崬傑傟傑偡丅

乮係侽乯僔僼僩僇僂儞僞 亅侾丆DDS_LP 偺儔儀儖傊栠傝孞傝曉偡

僔僼僩僇僂儞僞偺抣傪侾偢偮尭傜偟丄侽偵側傞傑偱DDS_LP偲偁傞儔儀儖傊栠傝丄DATA偺撉傒崬傒摦嶌傪孞傝曉偟傑偡丅

乮係侾乯娫愙傾僪儗僗億僀儞僞 亄侾

僶僢僼傽偺娫愙傾僪儗僗億僀儞僞傪亄侾偵偟偰丄師偺傾僪儗僗傪巜掕偟傑偡丅

乮係俀乯僨乕僞僇僂儞僞 亅侾丆DDS_SET 偺儔儀儖傊栠傝孞傝曉偡

僨乕僞僇僂儞僞偺抣傪侾偢偮尭傜偟丄侽偵側傞傑偱DDS_SET偲偁傞儔儀儖傊栠傝丄DATA偺撉傒崬傒摦嶌傪孞傝曉偟傑偡丅

乮係俁乯DATA = [H]

偡傋偰偺DATA偑DDS傊憲傝廔偊偨傜丄DATA怣崋儔僀儞傪乽俫乿偵愝掕偟偰偍偒傑偡丅

乮係係乯億乕僩偺岆摦嶌杊巭

偙偙偼丄乮係俁乯偲乮係俆乯偺傛偆偵丄BSF丆BCF側偳偺價僢僩憖嶌柦椷傪巊偭偰丄摨偠億乕僩偵弌椡偡傞応崌偵偼丄娫偵僟儈乕偲偟偰NOP柦椷側偳傪擖傟傞丅乮俁俉乯嶲徠

乮係俆乯STB = [L]

DDS傊偺STB怣崋儔僀儞傪[俴]偵偟傑偡丅偙偺偲偒丄STB偺棫偪壓偑傝偱丄撉傒崬傑傟偨僐儅儞僪丒僨乕僞偑幚峴偝傟丄DDS偺弌椡抂巕偐傜10MHz偺怣崋偑弌椡偝傟傑偡丅

乮係俇乯億乕僩偺岆摦嶌杊巭

偙偙偼丄乮係俆乯偲乮係俈乯偺傛偆偵丄BSF丆BCF側偳偺價僢僩憖嶌柦椷傪巊偭偰丄摨偠億乕僩偵弌椡偡傞応崌偵偼丄娫偵僟儈乕偲偟偰NOP柦椷側偳傪擖傟傞丅乮俁俉乯嶲徠

乮係俈乯STB = [H]

STB怣崋儔僀儞傪乽俫乿偵愝掕偟偰廔椆偟傑偡丅

乮係俉乯孞傝曉偟僨乕僞庴怣摦嶌偵擖傞

DDS偺愝掕偑廔椆偟偨屻丄PIC懁偺摦嶌偲偟偰偼丄師偺怴偨側愝掕僨乕僞偑庴怣偝傟傞偺傪懸偪傑偡丅

乮係俋乯DATA = [L]

乮俁俇乯偺暘婒柦椷偱丄侾價僢僩暘偺撉傒崬傑傟偨僨乕僞偑丄侽偩偭偨傜DDS傊偺DATA怣崋儔僀儞傪[俴]偵偡傞儖乕僠儞丅

乮俆侽乯DATA = [俫]

乮俁俇乯偺暘婒柦椷偱丄侾價僢僩暘偺撉傒崬傑傟偨僨乕僞偑丄侾偩偭偨傜DDS傊偺DATA怣崋儔僀儞傪[俫]偵偡傞儖乕僠儞丅

乮俆侾乯TABLE偺掕媊乮PC+OFFSET憡摉偺僔僼僩僇僂儞僞抣傪帩偭偰栠傞乯

丂丂丂丂PC亄OFFSET

僨乕僞僥乕僽儖偺僒僽儖乕僠儞偵棃傞偲丄僾儘僌儔儉僇僂儞僞偵丄Wreg偺抣乮僆僼僙僢僩乯偑壛嶼偝傟傑偡丅偦偺壛嶼寢壥傪僾儘僌儔儉僇僂儞僞偲偟傑偡偺偱丄偦偺僨乕僞僇僂儞僞乮傾僪儗僗乯偱巜掕偝傟偨抣傪帵偡傛偆偵側傝傑偡丅

ADDWF 丂丂PCL,F丂;僾儘僌儔儉僇僂儞僞偵丄Wreg偺抣乮僆僼僙僢僩乯傪壛嶼偟丄

丂丂丂丂丂丂丂丂丂丂丂丂丂偦偺壛嶼寢壥傪僾儘僌儔儉僇僂儞僞偡傞丅

乮俆俀乯僟儈乕僨乕僞

僨乕僞僇僂儞僞偺抣偼丄僔僼僩僇僂儞僞抣偑婰嵹偝傟偨僥乕僽儖偺埵抲娭學傪巜偟帵偟傑偡丅僨乕僞僇僂儞僞乮傾僪儗僗乯偱巜掕偝傟偨抣偺埵抲娭學傪懳墳偝偣傞偨傔偵丄偙偙偵僟儈乕傪擖傟偰偍偒傑偡丅

乮拲乯乮係俀乯偺暘婒柦椷偵傛傝丄僨乕僞僇僂儞僞偑侽偺偲偒僨乕僞偺撉傒崬傒儖乕僠儞傪敳偗偰偟傑偆偨傔丄偙偙偺傾僪儗僗埵抲偵僨乕僞傪婰嵹偟偰傕撉傒崬傒偑偝傟傑偣傫偺偱NOP偲偟偰偄傑偡丅

乮俆俁乯奺僨乕僞偵懳偡傞僔僼僩僇僂儞僞抣

昞俁偵奺俢俢俽愝掕僨乕僞偵懳偡傞僔僼僩僇僂儞僞抣傪帵偟傑偡丅

傑偢僠僢僾僙儗僋僩仌僐儅儞僪僨乕僞偱偡偑丄僠僢僾僙儗僋僩抂巕偼丄CS2丄CS1丄CS0偺俁價僢僩偱峔惉偝傟丄僐儅儞僪僨乕僞偼丄係價僢僩偱偡偺偱丄崌寁偱俈價僢僩暘偵側傝傑偡丅師偵廃攇悢僨乕僞偱偡偑丄Lower

Byte偼丂侽價僢僩栚乣俈價僢僩栚傑偱偺俉價僢僩暘丄Middle Byte偼丂俉價僢僩栚乣15價僢僩栚傑偱偺俉價僢僩暘丄Higher

Byte偼丂16價僢僩栚乣23價僢僩栚傑偱偺俉價僢僩暘丄偝傜偵丄24丆25價僢僩栚偱俀價僢僩暘偲偄偆傛偆偵丄僔僼僩僇僂儞僞抣傪愝掕偟傑偡丅

| 僨乕僞偺崁栚 | 僔僼僩僇僂儞僞抣 |

| 僠僢僾僙儗僋僩仌僐儅儞僪僨乕僞 | 俈 |

| 廃攇悢僨乕僞乮Lower Byte丗丂侽價僢僩栚乣俈價僢僩栚乯 | 俉 |

| 廃攇悢僨乕僞乮Middle Byte丗丂俉價僢僩栚乣15價僢僩栚乯 | 俉 |

| 廃攇悢僨乕僞乮Higher Byte丗丂16價僢僩栚乣23價僢僩栚乯 | 俉 |

| 廃攇悢僨乕僞乮24丆25價僢僩栚丂價僢僩偺抣偼忢偵侽乯 | 俀 |

乮俆係乯亙僼儗乕儈儞僌僄儔乕帪偺張棟亜

丂丂丂丂00001111 傪 Wreg 偵儘乕僪偡傞丆PORTB傊Wreg偺僨乕僞傪弌椡

丂丂丂丂(LED偺揰摂忬懺偱僄儔乕傪抦傜偣傞乯

偙偙偱偼丄僼儗乕儈儞僌僄儔乕偑敪惗偟偨偙偲傪妋擣偡傞偨傔丄 PORTB 壓埵係價僢僩偺

LED 傪揰摂偝偣傞傛偆偵偟傑偡丅

乮俆俆乯1昩偺僂僄僀僩傪擖傟傞

PORTB 偺 LED 偺揰摂帪娫傪侾昩娫偵愝掕偟傑偡丅偙偙偱偼丄抶墑僒僽儖乕僠儞傪巊偭偰偄傑偡丅

乮俆俇乯00000000 傪 Wreg 偵儘乕僪偟丄

丂丂丂丂PORTB傊Wreg偺僨乕僞傪弌椡(LED偺徚摂乯

揰摂偟偰偄偨俴俤俢傪徚摂偝偣傑偡丅

乮俆俈乯僟儈乕偺擖椡乮RCREG傪儕乕僪偡傞偲FERR偑僋儕傾偝傟傞乯![]()

亙僼儗乕儈儞僌僄儔乕帪偺張棟亜

庴怣帪偵僼儗乕儈儞僌僄儔乕偑敪惗偟偨応崌丄僼儗乕儈儞僌僄儔乕價僢僩FREE偑乽侾乿偲側偭偰偄傑偡丅

僼儗乕儈儞僌僄儔乕價僢僩傪儕僙僢僩偡傞応崌偵偼丄RCREG儗僕僗僞乮USART庴怣儗僕僗僞乯傪Wreg偵儘乕僪偡傞偲偄偆僟儈乕柦椷傪幚峴偟傑偡丅

乮俆俉乯僆乕僶乕儔儞僄儔乕偺僠僃僢僋乮1:僄儔乕,0:惓忢乯

丂丂丂丂僆乕僶乕儔儞僄儔乕偑側偗傟偽 MAIN 偺儔儀儖傊僕儍儞僾偡傞

庴怣僗僥乕僞僗偍傛傃僐儞僩儘乕儖儗僕僗僞偱偁傞RCSTA儗僕僗僞偺僆乕僶乕儔儞僄儔乕價僢僩乮OERR乯偺忬懺傪僠僃僢僋偟傑偡丅

BTFSS 丂丂RCSTA,OERR

乽RCSTA乿儗僕僗僞偺OERR價僢僩偑僄儔乕偺乽侾乿偩偭偨傜師偺柦椷傪僗僉僢僾偟丄僆乕僶乕儔儞僄儔乕偺僠僃僢僋傊恑傒傑偡丅

GOTO丂丂丂MAIN

僆乕僶乕儔儞僄儔乕偑側偗傟偽MAIN偺儔儀儖傊僕儍儞僾偟丄庴怣傪嵟弶偐傜傗傝捈偟傑偡丅

乮俆俋乯亙僆乕僶乕儔儞僄儔乕帪偺張棟亜

丂丂丂丂11110000 傪 Wreg 偵儘乕僪偡傞丆PORTB傊Wreg偺僨乕僞傪弌椡

丂丂丂丂(LED偺揰摂忬懺偱僄儔乕傪抦傜偣傞乯

偙偙偱偼丄僆乕僶乕儔儞僄儔乕偑敪惗偟偨偙偲傪妋擣偡傞偨傔丄 PORTB 忋埵係價僢僩偺

LED 傪揰摂偝偣傞傛偆偵偟傑偡丅

乮俇侽乯1昩偺僂僄僀僩傪擖傟傞

PORTB 偺 LED 偺揰摂帪娫傪侾昩娫偵愝掕偟傑偡丅偙偙偱偼丄抶墑僒僽儖乕僠儞傪巊偭偰偄傑偡丅

乮俇侾乯00000000 傪 Wreg 偵儘乕僪偟丄

丂丂丂丂PORTB傊Wreg偺僨乕僞傪弌椡(LED偺徚摂乯

揰摂偟偰偄偨俴俤俢傪徚摂偝偣傑偡丅

乮俇俀乯OERR偺儕僙僢僩乮價僢僩CREN 偺僋儕傾偵傛傝僋儕傾偡傞乯![]()

亙僆乕僶乕儔儞僄儔乕帪偺張棟亜

庴怣帪偵僆乕僶乕儔儞僄儔乕偑敪惗偟偨応崌丄僆乕僶乕儔儞僄儔乕價僢僩OERR偑乽侾乿偲側偭偰偄傑偡丅

僆乕僶乕儔儞僄儔乕價僢僩傪儕僙僢僩偡傞応崌偵偼丄RCSTA儗僕僗僞乮庴怣僗僥乕僞僗偍傛傃僐儞僩儘乕儖儗僕僗僞乯偺楢懕庴怣僀僱乕僽儖價僢僩乮CREN乯傪僋儕傾偡傞偙偲偵傛傝丄僆乕僶乕儔儞僄儔乕價僢僩乮OERR乯偑僋儕傾偝傟傑偡丅

乮俇俁乯楢懕庴怣傪嫋壜偡傞

愭偺僆乕僶乕儔儞僄儔乕帪偺張棟偱楢懕庴怣僀僱乕僽儖價僢僩乮CREN乯偑僋儕傾偝傟偰偟傑偭偰偄傞偺偱丄尦偺乽侾乿偵僙僢僩偟偰栠偟偰偍偒傑偡丅

乮俇係乯MAIN 偺儔儀儖傊僕儍儞僾偡傞

MAIN偺儔儀儖傊僕儍儞僾偟丄庴怣傪嵟弶偐傜傗傝捈偟傑偡丅

![]() 俢俢俽偺摦嶌妋擣

俢俢俽偺摦嶌妋擣

偦傟偱偼丄僷僜僐儞偐傜僔儕傾儖捠怣僜僼僩乽Acknowrich乿傪巊偭偰丄DDS傪僐儞僩儘乕儖偟偰傒傑偟傚偆丅Acknowrich偐傜偺僨乕僞揮憲偼丄僶僀僫儕儌乕僪偱峴偄傑偡丅

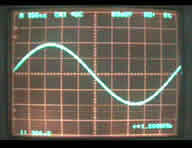

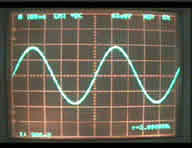

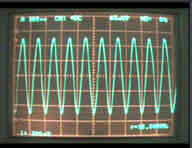

恾係偼丄Acknowrich傪巊偭偨DDS偺愝掕僨乕僞傪帵偟偰偄傑偡丅偦偺偲偒偺DDS偺弌椡攇宍乮恾俆乯傪僆僔儘僗僐乕僾偱尒偨偲偙傠偱偡丅俁夋憸偲傕斾妑偺偨傔丄僞僀儉儗儞僕偼摨偠偵偟偰偄傑偡丅偙傟傜偺寢壥偐傜丄僷僜僐儞偐傜DDS傪惂屼偱偒傞偙偲偑妋擣偱偒傑偟偨丅

|

|

|

| 乮侾乯僐儅儞僪俠 倖亖侾俵俫倸愝掕 |

乮俀乯僐儅儞僪俠 倖亖俀俵俫倸愝掕 |

乮俁乯僐儅儞僪俠 倖亖侾侽俵俫倸愝掕 |

| 恾係丏Acknowrich傪巊偭偨DDS偺愝掕 | ||

|

|

|

| 乮侾乯倖亖侾俵俫倸愝掕 | 乮俀乯倖亖俀俵俫倸愝掕 | 乮俁乯倖亖侾侽俵俫倸愝掕 |

| 恾係丏DDS偺弌椡攇宍 | ||

偙偺傛偆偵偟偰丄僷僜僐儞偐傜DDS僉僢僩傪惂屼偱偒傞偙偲偑傢偐傝傑偟偨丅偟偐偟丄僔儕傾儖捠怣僜僼僩乽Acknowrich乿偐傜DDS偺愝掕僨乕僞傪擖椡偡傞偺偼壗偐偲晄曋偱偡丅偦偙偱丄乽師傊乿偼愱梡偺DDS惂屼僜僼僩傪VisualBasic偱奐敪偟偰偄偔偙偲偵偟傑偡丅

|

|

|

|